Sigrity er det mest velprøvde verktøyet for modellering, signal- og strømintegritetsanalyse for PCB og IC.

Sigrity gir høyhastighetsdesigneren alt han trenger. Det er den kraftigste, avanserte sammenkoblingsmodelleringen, signal- og strømintegritetssimuleringen for PCB og IC.

Med Cadence® Sigrity™ PowerDC™, med den ekstra nøyaktigheten av elektrisk/termisk samsimulering, får du forsikringen om at din PDN fungerer som forventet. Med PowerDC kan du enkelt lokalisere tilfeldige spenningstap, høye strømtettheter, via med for høye strømmer og termiske hotspots. Alle disse effektene kan påvirke kvaliteten på designet betydelig og begrense produktets levetid.

Med Cadence® Sigrity™ OptimizePI™ får du innsikt i hvordan PDN-frekvenskarakteristikken ser ut for hver enkelt komponent, inkludert plandesign og plassering i stablen, frakobling, deres ruting og plassering, samt ruting fra forsyningsplaner til komponenter. Plasserte frakoblinger kan også optimaliseres med tanke på pris vs. ytelse og verifiser EMI-ytelse ved å måle impedans for selvvalgte steder på oppsettet.

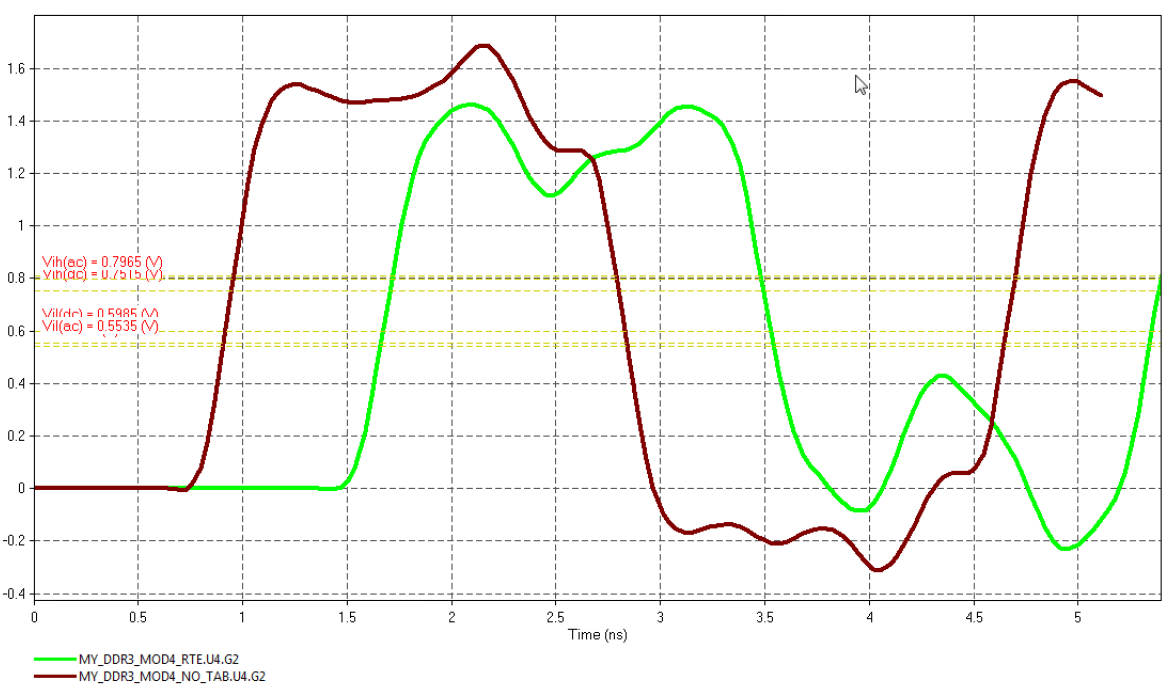

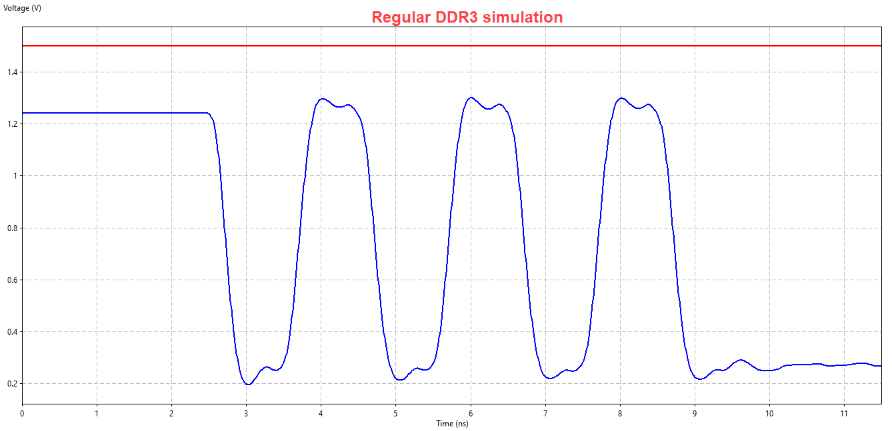

Simultaneous switching noise (SSN) kan endre timingen på et minnegrensesnitt. Med Sigrity™ Power-Aware SI får du en komplett løsning for å analysere kildesynkrone grensesnitt brukt til f.eks. DDR3 og DDR4 minnegrensesnitt. Power-Aware SI inkluderer både verktøy for layoututvinning av stier og forsyninger samt intuitive simuleringsverktøy for parallellbussanalyse som kan generere rapporter med informasjon om tidsmarginer som oppfylles i henhold til JEDEC-standarden.

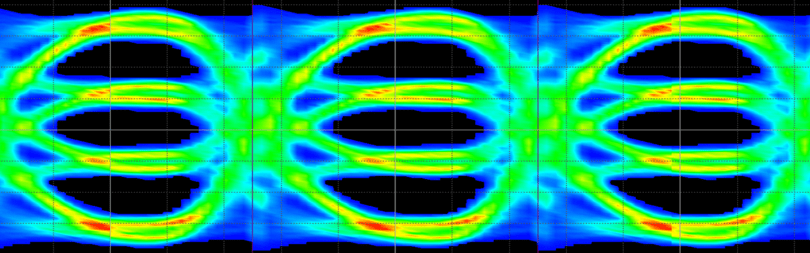

Utfør brikke-til-brikke-analyse på dine High-Speed SerDes-grensesnitt, som PCI Express® (PCIe®), HDMI, SFP+, Xaui, Infiniband, SAS, SATA og USB med industristandard IBIS AMI-modeller. Du kan utføre pre-layout-analyser ved å bruke maler og underveis legge til modeller av komponentpakker, koblinger og oppsett for å gjenspeile hele grensesnittet. Simuleringer kan brukes til å identifisere krysstaleproblemer og vise ikke bare signalene i grensesnittet, men også signaler etter klokke og datagjenoppretting (CDR), som er beskrevet i IBIS AMI-modellen. Ved å simulere hele grensesnittet med millioner av biter, kan den totale bitfeilfrekvensen (BER) beregnes for å bestemme om jitter- og støynivåer er innenfor spesifiserte toleranser.