Book møde

Menu

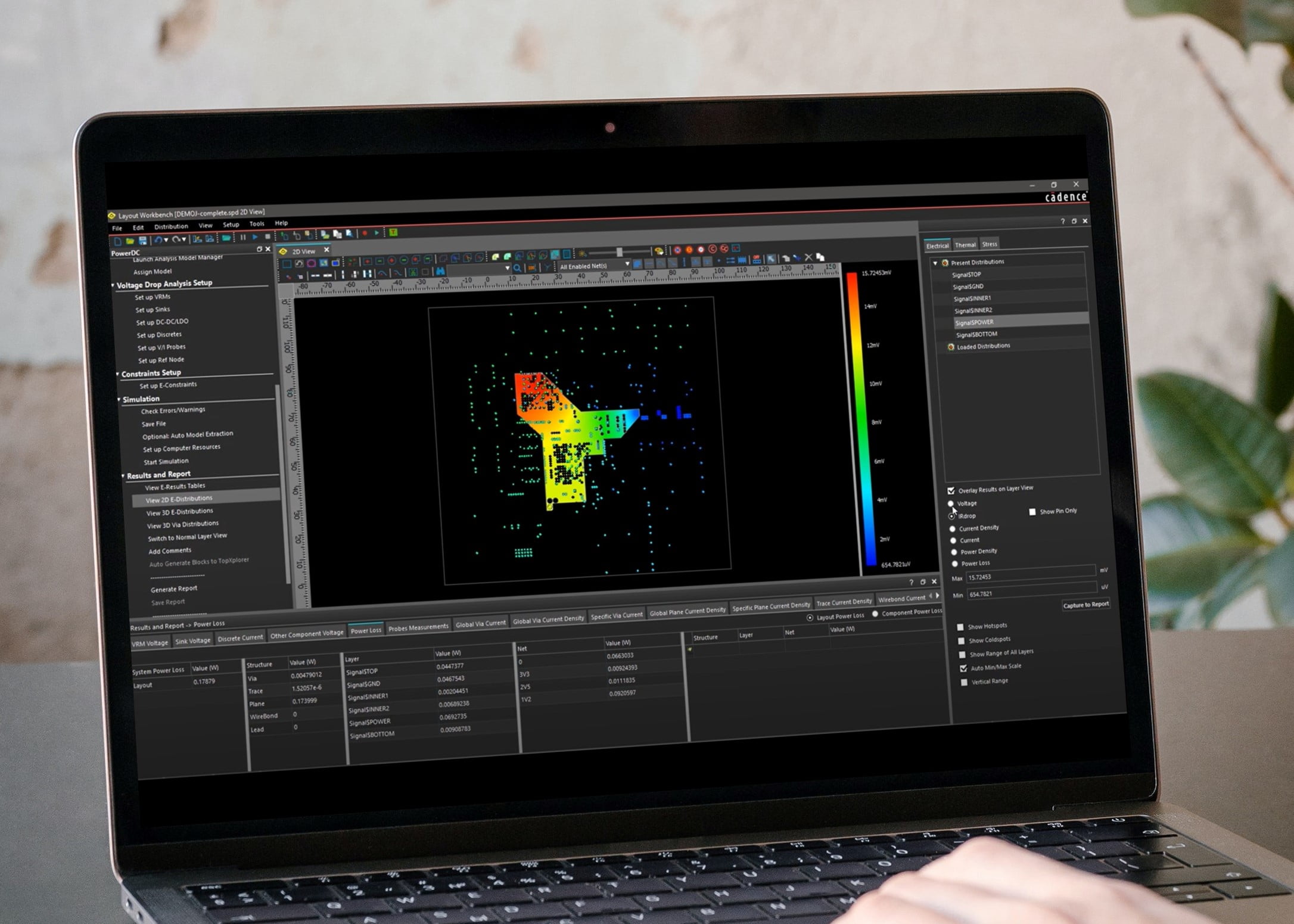

Med Cadence® Sigrity™ PowerDC™ kan du nemt lokalisere utilsigtede spændingstab, strømtætheder, via med for høje strømme og termiske hotspots. Alle disse effekter kan påvirke designets kvalitet markant og begrænse produktets levetid.

PowerDC™ miljøet giver hurtig og præcis DC-analyse for IC-pakker og PCB'er. Med fokus på både pre- og post-layout applikationer, giver PowerDC adgang til kraftfulde funktioner, herunder optimering af sense line placering og bekræftelse af forenklede design rule checks (DRC), der arbejder sammen med den hurtigst tilgængelige simulering for at støtte designforbedringer uden unødvendige omkostninger og tidsforbrug.

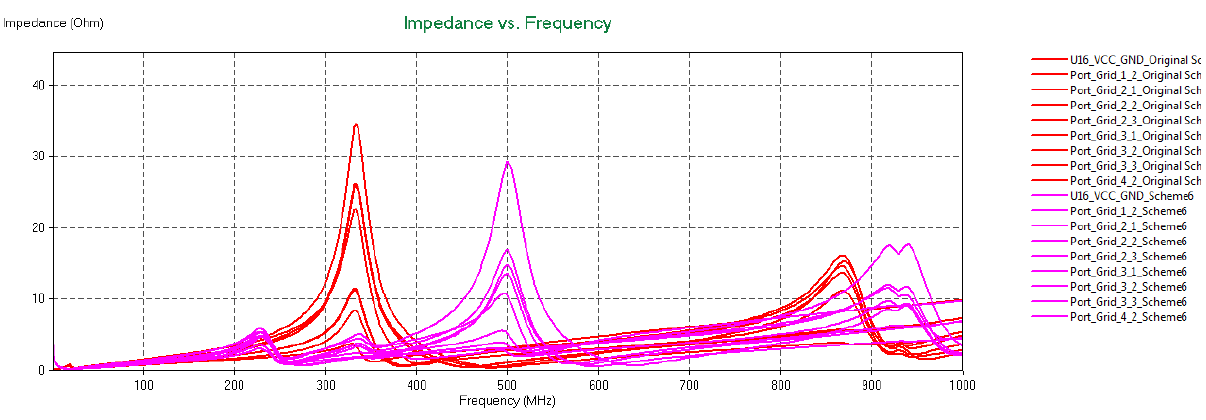

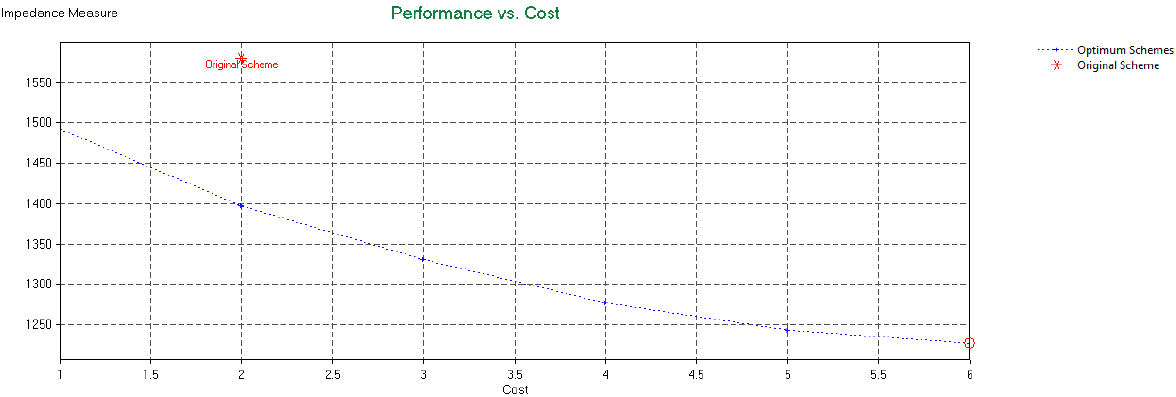

Med Cadence® Sigrity™ OptimizePI™ får du indsigt i, hvordan PDN frekvenskarateristikken ser ud for hver enkelt komponent - inklusiv planers udformning og placering i stackup, afkoblinger, deres routing og placering samt routing fra forsyningsplaner til komponenter. Der kan også optimeres på placerede afkoblinger mht. pris vs. performance og verificer EMI performance med måling af impedans for selvvalgte placeringer på layoutet.

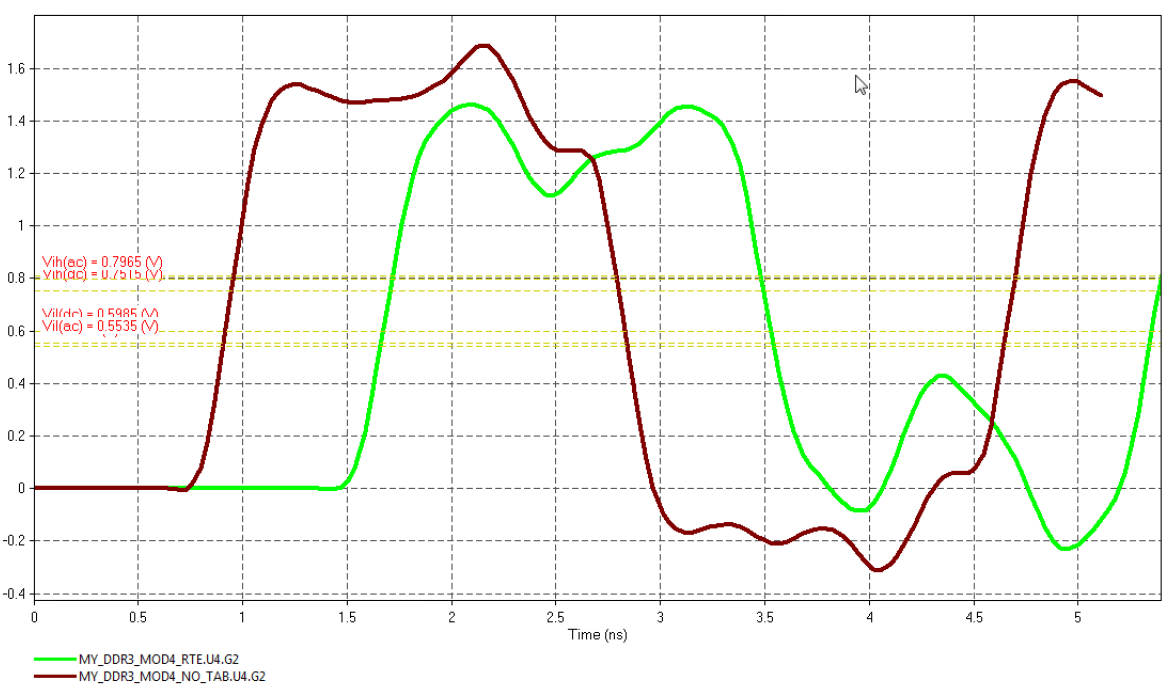

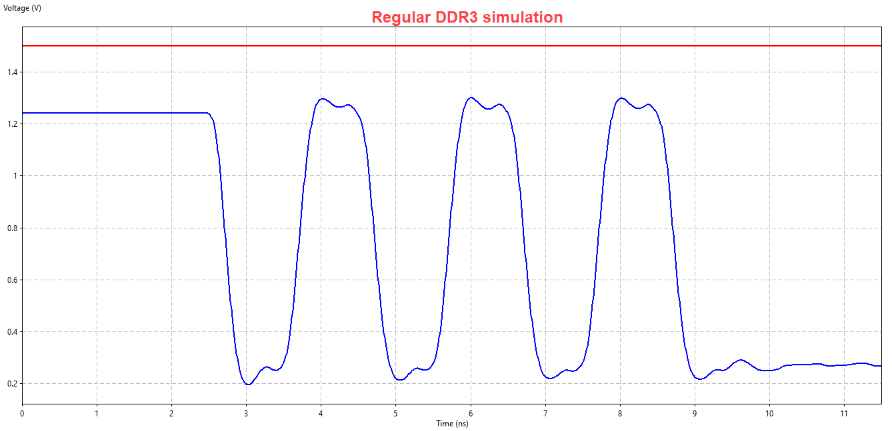

Simultaneous switching noise (SSN) kan ændre i timingen på et memory interface.

Med Sigrity™ Power-Aware SI får du en komplet løsning til analyse af source-synchronous interfaces, der anvendes til f.eks. DDR3- og DDR4 memory interfaces. Power-Aware SI omfatter både værktøjer til layout ekstraktion af baner og forsyninger, samt intuitive simuleringsværktøjer til parallel bus-analyse, der kan genere rapporter med information om tidsmargener bliver opfyldt i henhold til JEDEC standarden.

Med den eksponentielle stigning i forbruger-/IoT-enheder overføres zettabytes af data hvert år, og systemdesigns bliver typisk bedt om at fordoble overførselshastighederne hvert andet år.

Design og analyse af multi-gigabit serielle links skal være tilgængeligt på ingeniørens skrivebord.

Vi udbyder teknologi, der hjælper dig med at analysere og optimere alle sektioner af det serielle link.

Transceivere og alle forbindelser, der forbinder chips, pakker, printplader og stik, kan modelleres og simuleres for at bekræfte, at de serielle links i dit produkt vil opfylde specifikationerne.

Denne avancerede tilgang til analyse er essentiel for at forstå og forbedre SI/PI i højhastighedsforbindelser, som ofte findes i avancerede elektroniske systemer, såsom cloud-servere, telekommunikationsudstyr og forbrugerelektronik.